Key Performance Specifications

- LPDDR5X-9600

- DDR5-4800

- LPDDR4X-4267

- ClockSafe™

- 1G-sample acquisition depth

- Programmable probe termination

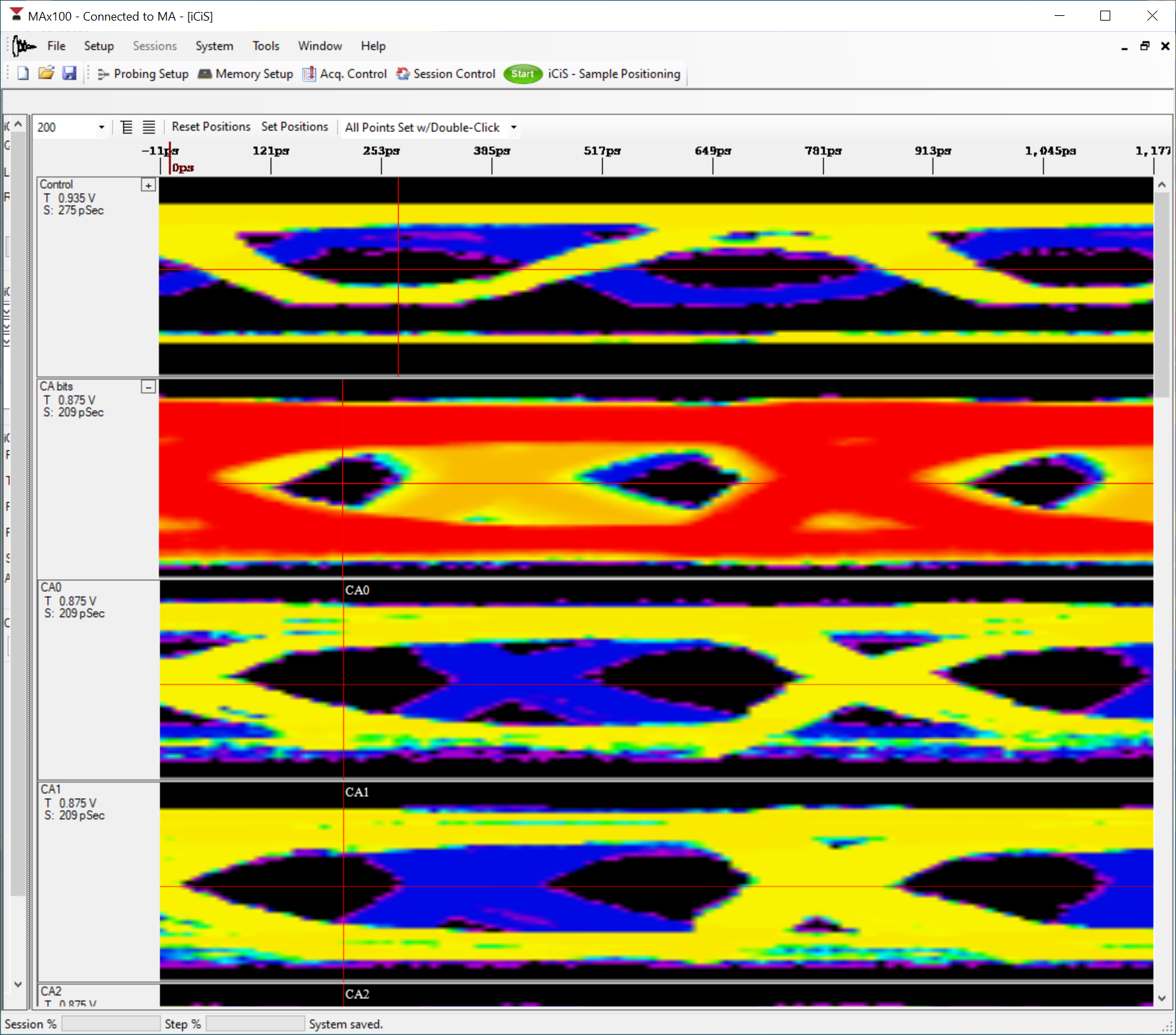

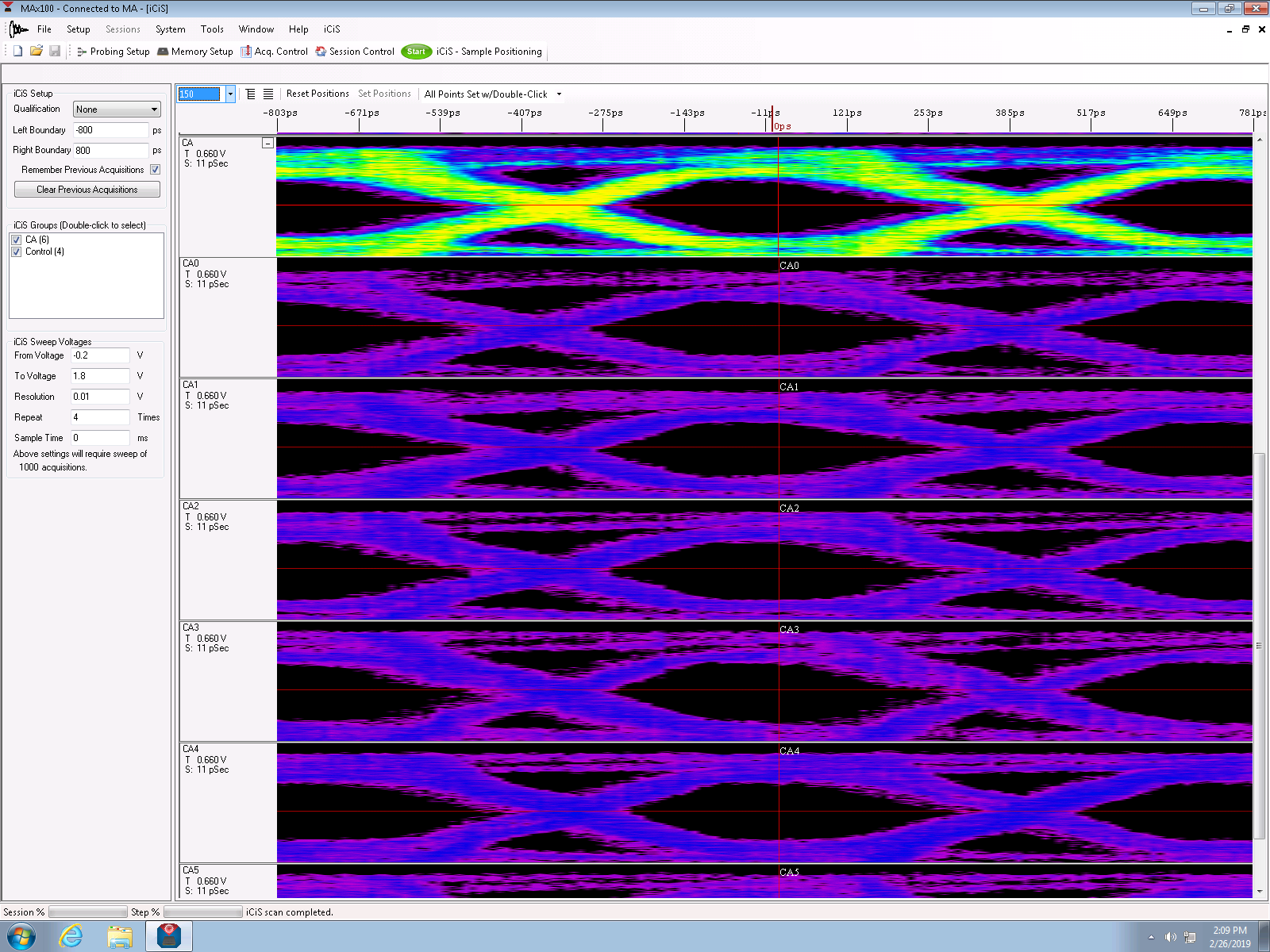

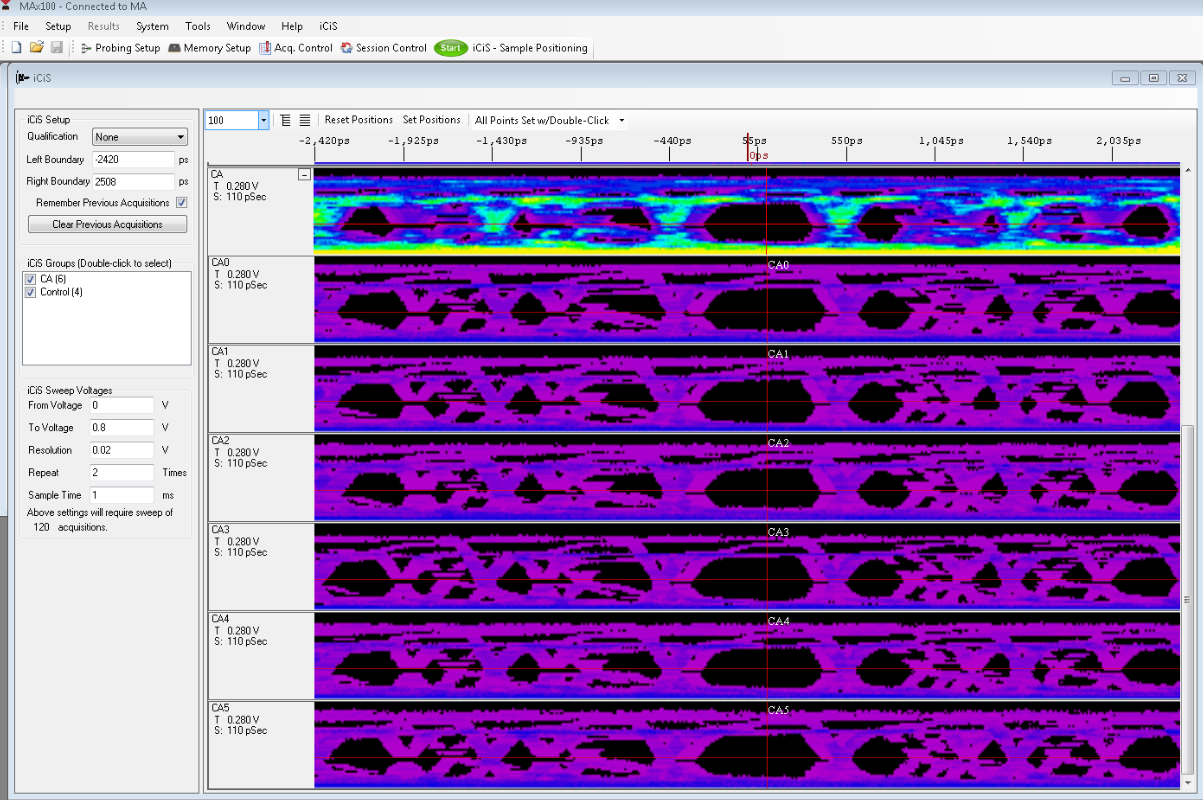

- 11ps x 10mV analog characterization (iCiS™)

- Real-time smart single frequency or 16 frequency analysis

- Real-time memory performance metrics

- Real-time memory compliance margins and validation

- Trigger in and trigger out

Key Features

- Application software ready for bench, remote-to-lab or offline operation

- Application includes advanced listing, waveform, tables and charting

- Turnkey setup, including automated MRW capture and analysis

- Patented interposer/probe designs

- Analyze thousands of real-time memory parameters

- Full featured, industry standard trigger system

- Automated analysis runs for everything from detailed setup information, to quick summary runs, to in-depth extended data logging or margin testing runs

- ClockSafe™: Continuous analysis across clock stops and clock frequency changes

- Analog eye characterization on 20-channels simultaneously at 11ps x 10mV

- Correlate with an oscilloscope for memory DQ data capture

- Integrated Windows 10 Controller

Applications

- DDR5, LPDDR5, LPDDR5x, LPDDR4, LPDDR4x and/or LPDDR3

- Memory validation and debug

- Monitoring bus traffic

- Bus traffic measurement

- Optimization of memory performance

- Analog insight

- JEDEC JESD79-5 rates to DDR5-4800

- JEDEC JESD209-5 rates to LPDDR5X-9600

- JEDEC JESD209-4 rates to LPDDR4X-4267

- JEDEC JESD209-3 rates to LPDDR3-2133

Results Overview

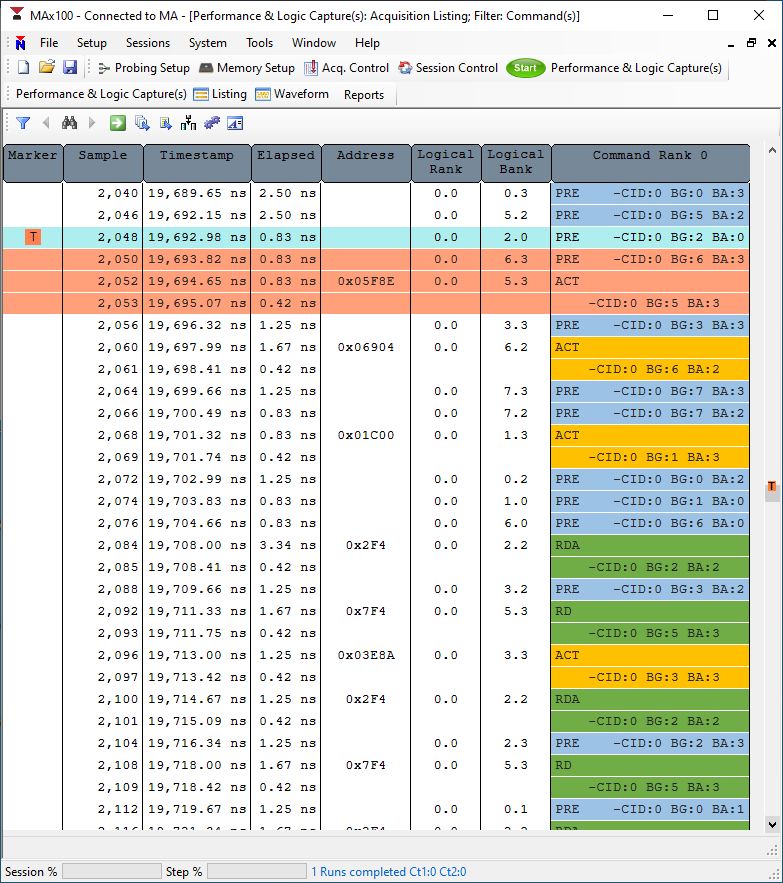

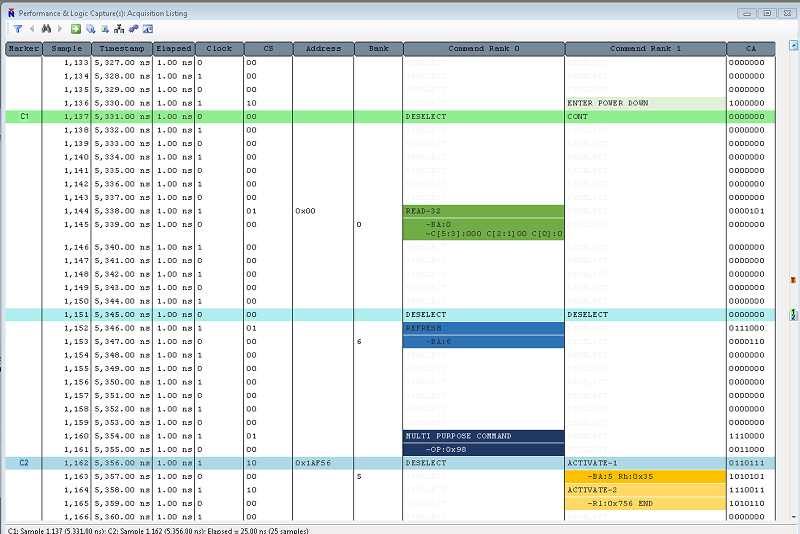

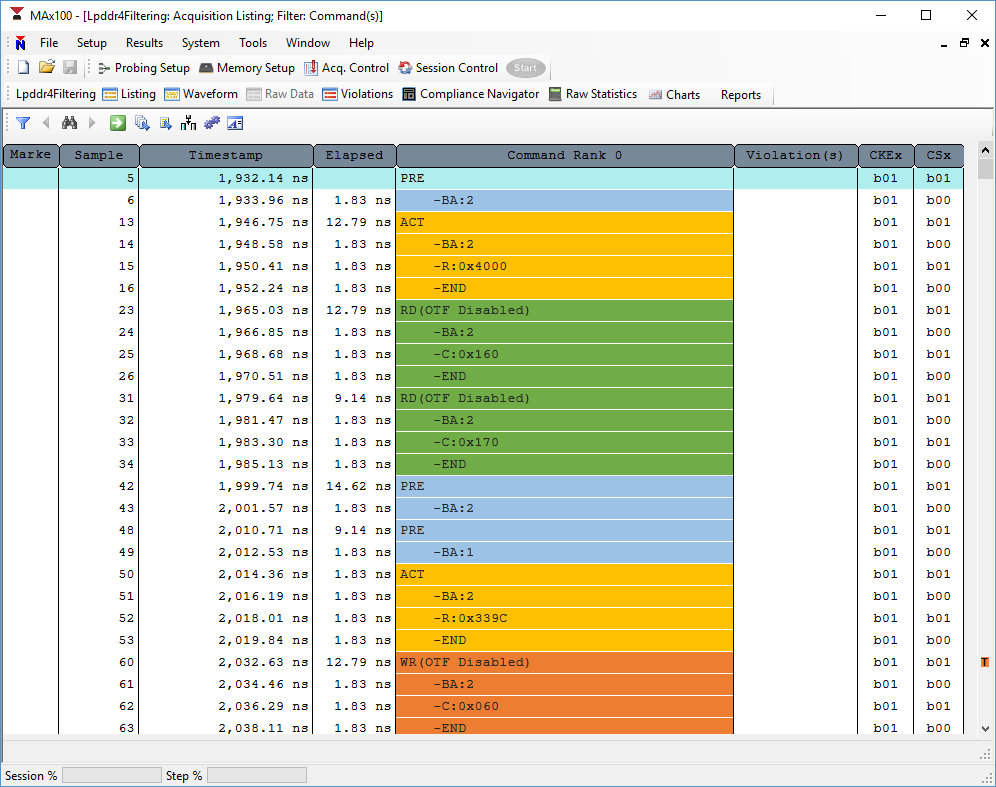

State Capture

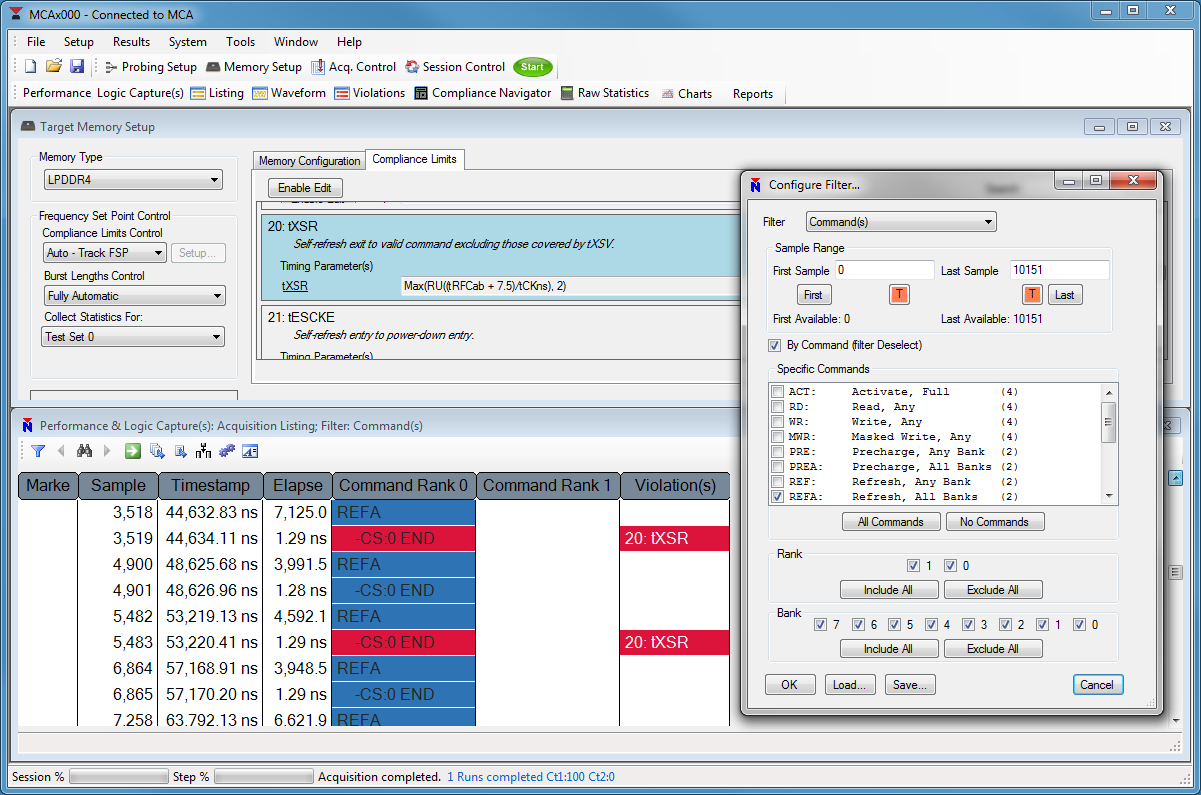

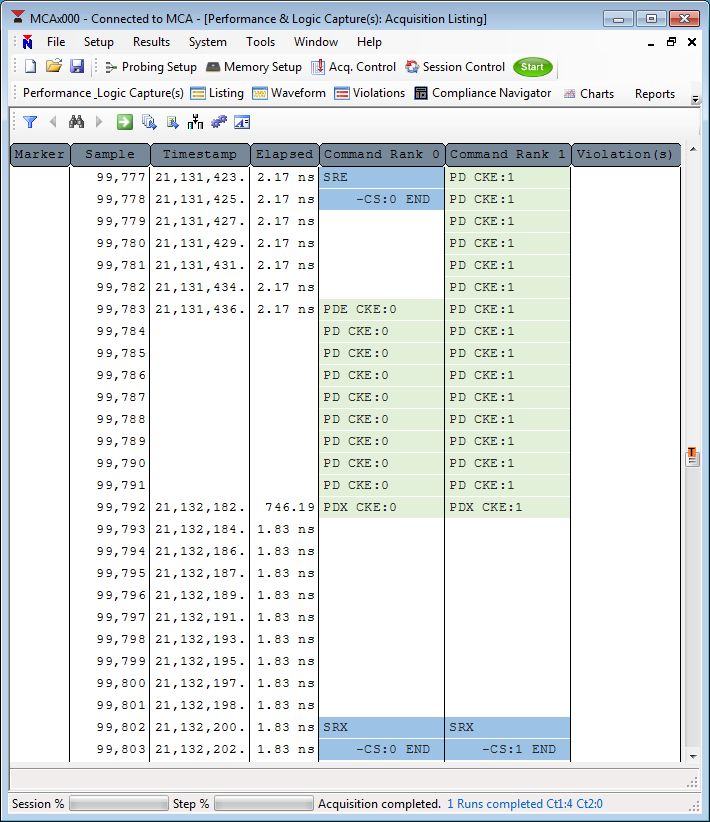

State capture results include continuous traffic around one or more events of interest. The traffic, which may consist of time, bus commands, bus addressing, margin violations, and trigger events, is presented in listing or waveform displays. State capture depths from one hundred samples to one billion samples is available. Advanced acquisition controls monitor and respond to the continuous traffic in real-time to best utilize the state capture memory. Advanced post-capture search and filter can quickly parse the acquisition store.

Real-time Continuous Analysis

Real-time analysis provides data results during and after analysis runs which may be extremely long (days) or very short (nano-seconds). During the run, analysis is continuous and in real-time. Any event that occurs during the run is captured and analyzed.

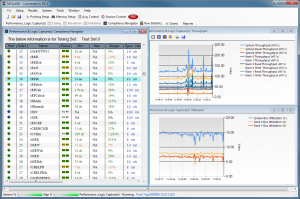

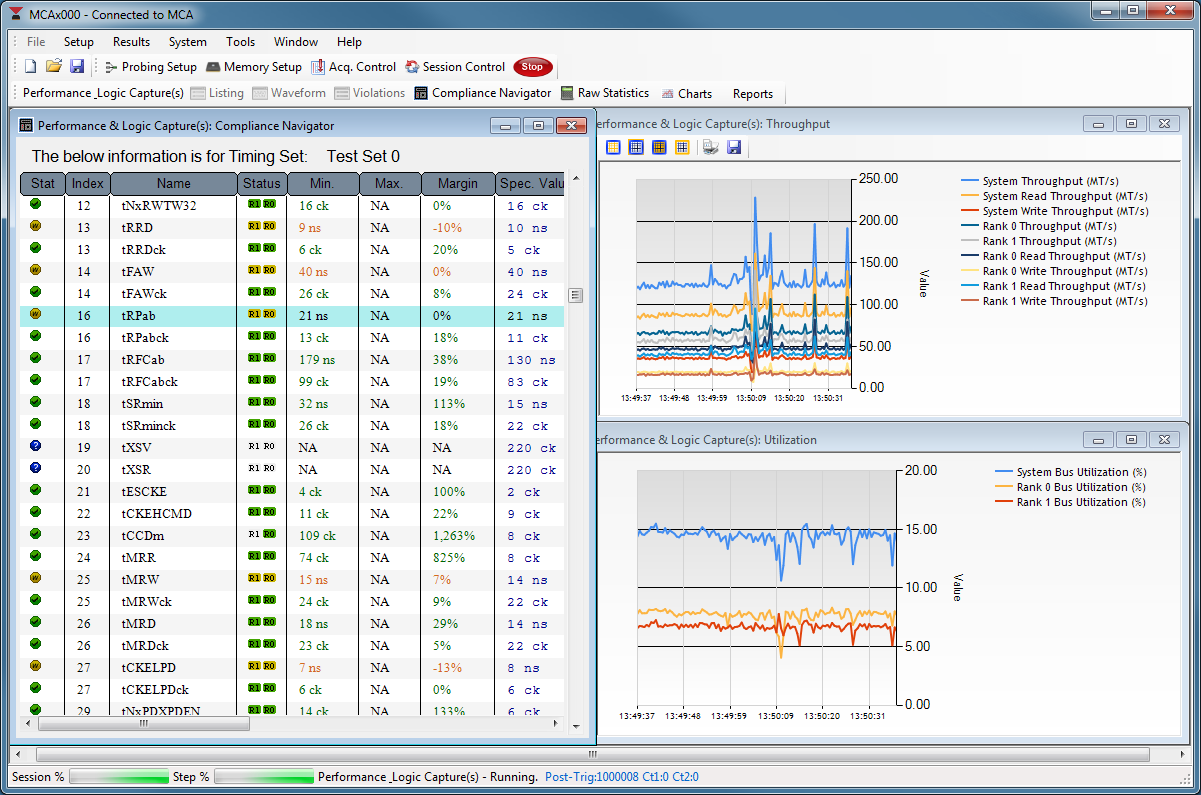

Performance

Memory performance metrics include real-time margin metrics and margin violations. For each margin test, results indicate test coverage, observed margin values, as well as flags indicating margin violations. All data is continuously acquired in real-time with results updates continuously while the analyzer is still running. Memory performance metrics also include continuous real-time charting of bus performance characteristics such as throughput, utilization, power management, and more.

True Analog Visibility

iCiS™ provides detailed and invaluable insight of signal quality and expected performance for data acquisition you can trust.

Automated Analysis

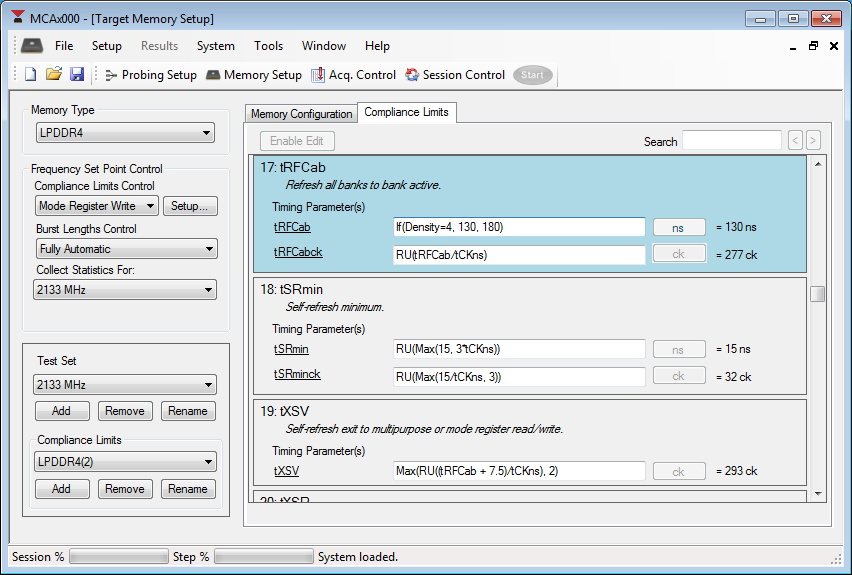

Analysis is automated and continuous from the time the user clicks the Start button until the analysis session completes. While running, the session updates the application with real-time results. In the MA5100 Performance Metrics image you can see real-time margins for all compliance parameters as well as a chart of read/write bus throughput. In this example, the analyzer is configured to continuously monitor acquire data until the first occurrence of a compliance violation occurs. That’s three simultaneous measurements, each collecting/monitoring real-time data.

ClockSafe™

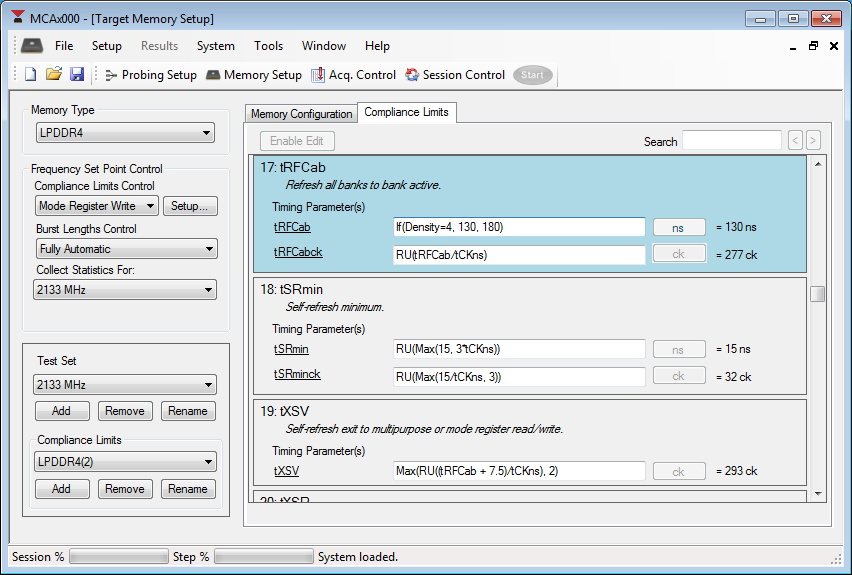

The memory clock stops and changes frequencies during initialization and calibration. It may also stop and change frequencies during normal operation. ClockSafe™ provides continuous acquisition across these clock stops and frequency changes through a robust acquisition interface that can handle any clock frequency from 0MHz to 2.4GHz. ClockSafe™ also provides continuous analysis by performing real-time measurements in nanoseconds (ns). This is critical for accurate measurements which would otherwise be corrupted when the clock stopped or changed frequencies. Analysis in nanoseconds (ns) is specified for a number of measurements in the JEDEC specifications. ClockSafe™ ensures these measurements are performed, not only correctly, but also accurately.

Smart Sixteen Frequency Analysis

Why analyze one frequency at a time when you can analyze all of them at once?

With aggressively changes frequencies, LPDDR5 and LPDDR4 presents a challenging analysis environment for most other analyzers but not for the MA5100 with Smart Sixteen Frequency Analysis and ClockSafe™.

With the push of a button the MA5100 starts acquiring and analyzing the memory bus in real-time. When a frequency change occurs, the analyzer responds, in real-time, collecting statistics for any one or all frequencies as well as margin testing (looking for violations) specific to each, of up to sixteen, independent frequencies and sixteen sets of margin limits. What does this mean for our users? It means they can run the analyzer once and verify the protocol and margins for every command – missing nothing – in real-time for every frequency.

Reliable Connection

DDR5, LPDDR5(X), LPDDR4(X) and LPDDR3 interposers and probes provide connection between the analyzer and the target while preserving analog signal characteristics.

Attachment Service

DDR5, LPDDR5(X), LPDDR4(X) and LPDDR3 memory components are available in a variety of packages. Many packages are very fine pitch BGA which typically live on densely populated targets. This presents a challenging probing environment and an opportunity to provide our expert services. We provide attachment services for all of our component/package interposers so that our customers are up and running quickly and reliably.